### RESEARCH ARTICLE

OPEN ACCESS

# An ANN Based Capicitor Voltage Balancing Method For Neutral Point Clamped Multi-Level Inverter

P.J.S. Praveen, Narendra Bavisetti, V.Satyanarayana

PG ScholarDepartment of EEERamachandra College of Engineering, Vatluru(V),Pedapadu(Md), EluruAndhra Pradesh, India

Assistant Professor Department of EEERamachandra College of Engineering, Vatluru(V),Pedapadu(Md), EluruAndhra Pradesh, India

Associate Professor Department of EEERamachandra College of Engineering, Vatluru(V),Pedapadu(Md), EluruAndhra Pradesh, India

### Abstract

Multi-level inverters are became popular for usage in medium voltage, low voltage power applications due to flexibility in control and better performance characteristics in terms of harmonic regulation. Neutral point clamped are popular as they require less number of sources as their input when compared with their counter parts i.e. cascaded multi-level inverters and found to be reliable when compared with flying capacitor based multi-level inverters. But when neutral clamped technologies are used for generation of three-phase voltages, the capacitors that are connected at input side experiences imbalance in their voltages, this makes neutral point clamped multi-level inverters less reliable. In the proposed work an attempt is made to study circuits that balances the capacitor voltages and a scheme is investigated for balancing the capacitor voltages. Method proposed in [1] uses PID controller for balancing the capacitor voltages. In this project PI based control scheme and artificial neural network (ANN) based control scheme for the front end circuit shown in [1] are designed for achieving balance among the capacitor voltages. The proposed control scheme is simulated with the help of Simpowersystems block set and neural network toolbox of MATLAB software for different load conditions. Results obtained from ANN based controller and PI controller are presented.

*Keywords*—DC Volatge balance, Neutral Point Calmaped Multilevel Converter, Multilevel Converetrs, ANN based Controller.

### I. INTRODUCTION

Multilevel converters (MLC) have the later years been looked upon as a decent choice for medium- and high-voltage applications. It had been first given in [2]. Before the introduction of multilevel converters the standard answer has been to attach semiconductors asynchronous switches to resist the high voltages. This needs fast change to avoid unequal voltage sharing between the devices that may lead to a breakdown. MLC have the advantage of clamping the voltages that prevents the necessity of quick change. MLC even have a smoother output voltage than traditional two-level converters.

Multilevel inverters have an arrangement of switches, capacitors and voltage sources for production of stepped sine wave output at their output terminals. By using proper control, the switching devices can generate stepped output voltages with low harmonic distortions. Multilevel inverters have drawn tremendous interest in the field of medium, highvoltage and high-power applications because it has some advantages: it can realize high voltage and high power output using low-voltage switches without use of transformer and dynamic voltage balance circuits. With increased output levels reduced harmonics are produced. Most commonly used multilevel inverter configurations are diode-clamped, capacitor-clamped and cascaded H-bridge inverters.

Among the available basic multilevel inverter configurations, the problem of voltage unbalance of dc link capacitors exist in diode-clamped inverter topology. Due this reason usage of diode-clamped inverters for production of high voltage levels is limited.

Diode-clamped converter topology is also known neutral-point-clamped converter (NPC). This as topology was proposed in the early 80's by [9], multilevel power converters are being employed in the industry, mainly in high-power applications [10]. Bidirectional power flow, near sinusoidal currents and high efficiency are some of the most attractive features that these power conversion systems have. Each phase of a multilevel converter can generate more than two different voltage levels. When compared with the conventional two-level converter, the generated voltages have more possibility to approach the sinusoidal waveforms, which reduces the harmonic distortion [11]. But increase of number of voltage levels leads to a higher complexity in converter structure and require additional dc-link capacitors in topologies such as the NPC. Concerning these capacitors, balancing of their voltages according to operating point is one of the major technical challenges of multilevel converters.

In a NPC based three-level inverter, the DC-link voltage is shared by the capacitors, Unbalance of neutral voltage is caused due to the current flowing into and out of neutral point. Unbalance of potential of neutral point is an inherent problem in NPC inverters. Neutral point voltage unbalance can be attributed to non-uniform voltage distribution of DC-link capacitor voltages, operating conditions and load types. Unbalance in neutral point voltage increases harmonics in output voltage, may drift the output voltage to an unacceptable level, which in turn lead to damage of the switching devices and filter capacitors [17]-[21]. In literature various control strategies have been proposed to maintain the balance of neutral point voltage. A zero sequence signal is added to modulation waves in Sinusoidal Pulse Width Modulation Scheme (SPWM) in order to balance the neutral point voltage [22]. This requires separate measuring circuit for measurement of power factors and phase angle of load voltages and currents. To balance the voltage of dc link series capacitors, several approaches have been proposed. Some of them are: 1) Using separate dc sources, [3], [4] 2) Adding some auxiliary balancing circuits [5], [6] and 3) Improving the control method by selecting redundant switching states [7], [8].

By using auxiliary circuits, the transferred current or power accurately controlled, these circuits require additional feedback control strategies, so the control of these converters becomes more complicated, and this feature makes these inverters less reliable for usage in medium, high –voltage applications.

A scheme is proposed in [23] uses less number of measuring quantities for design of control circuit but the drawback is instantaneous control is not possible. Scheme proposed in [24] is valid only for those circuits in which the change in neutral voltage is proportional to change in carrier signals. So, a threelevel boost converter (TLBC) is presented and used as an active front end circuit for a three-phase five level neutral point clamped multilevel inverter. The switches shown in circuit are controlled with PI based PWM control scheme. The TLBC circuit is consisting of three-level boost converter and four capacitors. The capacitor voltage balancing in the five-level NPC MLI is done by TLBC i.e., all the capacitor voltages are equal to the 1/4th of source voltage. But for betterment working and better quick response and settling time of capacitor voltages artificial neural network (ANN) based switching scheme is used in place of PI controller.

The working of NPC based MLI is discussed in section II followed by working of TLBC. The TLBC actually consists of PI controller for capacitor voltage balancing which in turn replaced by an ANN. The working of TLBC and ANN are also discussed in section II. Section III presents modeling aspects of ANN based switching scheme.

### II. PRINCPLE & OPERATION

### A. Neutral point Clamped Multi level Inmverter – Principle & Operation

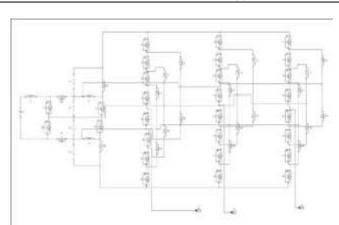

A NPC based multilevel inverter mostly consists of (m-1) capacitors on the dc bus and produces m levels on the phase voltage. The following Fig.2.1 shows you the three-phase five-level NPC. The order of the switches is  $S_1$ ,  $S_2$ ,  $S_3$ ,  $S_4$ ,  $S_5$ ,  $S_6$ ,  $S_7$  and  $S_8$  and as it is a five-level converter it consists of 4 capacitors namely  $C_1$ ,  $C_2$ ,  $C_3$  and  $C_4$ . For a dc bus voltage  $V_{dc}$ , the voltage across each capacitor is  $V_{dc}/4$ . So an m-level inverter leg requires (m-1) capacitors, 2(m-1) switching devices and (m-1) (m-2) clamping diodes.

The figure shown in 2.1 is one leg of the threephase five-level NPC. The arrangement of steps to blend the five-level voltages is as follows:

- For an output voltage level  $V_{ao} = V_{dc}/2$  turn on all upper half switches  $S_1$  through  $S_4$ .

- ♣ For an output voltage level V<sub>ao</sub> =V<sub>dc</sub>/4, turn on three upper switches S<sub>2</sub> through S<sub>4</sub> and one lower switch S<sub>5</sub>.

- ♣ For an output voltage level V<sub>ao</sub> =0, turn on upper two switches S<sub>3</sub> and S<sub>4</sub> and two lower switches S<sub>5</sub> and S<sub>6</sub>.

- For an output voltage level V<sub>ao</sub> =-V<sub>dc</sub>/4, turn on one upper switch S<sub>4</sub> and three lower switches S<sub>5</sub> through S<sub>7</sub>.

- For an output voltage level  $V_{ao} = -V_{dc}/2$ , turn on all lower switch S<sub>5</sub> through S<sub>8</sub>.

Fig.2.1:Schematic circuit of Three-level boost chopper based 5-Level NPC inverter.

The following table 2.1 shows the NPC based MLI output voltage level for their relevant switching samples. State condition 1 means the switch is on, and state condition 0 means the switch is off. It should be noticed that each switch is turned on only once per cycle and there are four complementary

switching pairs in each cycle. The pairs mentioned here are for one leg of the three-phase five-level NPC. They are (S1, S5), (S2, S6), (S3, S7) and (S4, S8).thus, if one of the complementary switches is on, then the other switch of the same pair must be off. Four switches are at on state always at the same time.

| Pole Voltage       | Switching states |       |       |       |       |       |       |                |

|--------------------|------------------|-------|-------|-------|-------|-------|-------|----------------|

| (V <sub>AO</sub> ) | $S_1$            | $S_2$ | $S_3$ | $S_4$ | $S_5$ | $S_6$ | $S_7$ | S <sub>8</sub> |

| Vdc/2              | 1                | 1     | 1     | 1     | 0     | 0     | 0     | 0              |

| Vdc/4              | 0                | 1     | 1     | 1     | 1     | 0     | 0     | 0              |

| 0                  | 0                | 0     | 1     | 1     | 1     | 1     | 0     | 0              |

| -Vdc/4             | 0                | 0     | 0     | 1     | 1     | 1     | 1     | 0              |

| -Vdc/2             | 0                | 0     | 0     | 0     | 1     | 1     | 1     | 1              |

Table.2.1: Switching state of the five-level NPC:

This circuit configuration provides excellent control over power flow and most preferred study in real time applications [25-30] which addresses the important issue of unequal allocation of voltages in clamping diodes in neural point clamped converters with higher number of levels.

# B. Three-level Boost Converter(TLBC)-Working and Operation

It has long been familiar that, for the NPC inverter with more than three levels, a static front-end capacitor voltage balancing method is only achievable if the modulation index is limited to about 60% of its maximum value for loads with a typical 0.8 power factor [38]–[41].

If the modulation index is raised greater than this worth, the inner capacitors gradually discharge, and sooner or later, the inverter output converges at three stages [42]. To beat this drawback, a multilevel inverter can also be offered with the remote dc sources [37], [43] similar to the outside circuit as the active front-end solution of dc-link capacitor balancing [38], [42], [44]–[47], making use of

balancing circuit by transferring charge from one capacitor to another capacitor to equilibrium stage [33], [34], [48] or the change of the pulse width modulation (PWM) switching sample [31], [32], [35],[36], [39],[49]–[53].

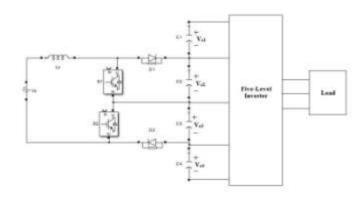

Many authors proposed PWM techniques for capacitor voltage balancing to avoid additional cost when using active front end balancing circuit. This process is observed to have problem on the range of operation with the changing of the power factor and modulation index [40], [41] and [50]. Once a PWM technique is employed for dc-link capacitor voltage balancing, solving problems such as total harmonic distortion, common-mode voltage cancellation, and leakage current elimination with the same procedure shouldn't be feasible. It has been pointed out within the introduction of [54] that capacitor voltage balancing and common mode voltage cancellation cannot be fulfilled concurrently in a multilevel inverter. On this paper, a three-level boost converter (TLBC) is used to supply a five-level neural-pointclamped inverter as proven in Fig.2.2.

Fig.2.2:Schematic of Three-Level boost chopper for 5-Level NPC inverter.

In energy conversion approach, a boost chopper is recurrently used as a result of its easy topology and control method [44]–[46], [55]. The TLBC has advantages in high power applications comparable to reduced switching losses and low reverse recovery losses of the diode [44]. With decreased inductor current ripple in TLBC, a smaller size inductor can be utilized in TLBC compared to the typical boost converter [47].

DC-link capacitor voltage balancing is carried out utilizing a blend of active front-end and balancing circuits. TLBC is used to balance the two inner capacitors, C1 and C2, and another balancing circuit is used to balance the outer capacitors, C1 and C4. The capacitor voltage balancing is done by transferring the charge from inner capacitors to the outer capacitors. The proposed configuration is compatible for a grid-related PV approach which operates in unidirectional power flow. The prototype is verified for various load power aspect conditions to assess its performance at a high modulation index.

# C. Balancing of capacitor voltages of TLBC using ANN

#### 1) Introduction to ANN

Work on synthetic neural network has been motivated from its inception by the consciousness that the human brain computes in a wholly specific method from the typical digital computer [56]. The brain is an extremely difficult, nonlinear and parallel information processing system. It has the potential to prepare its structural elements, often called neurons, to be able to participate in specific computations regularly rapid than the quickest digital computer in existence in these days. The brain sometimes accomplishes perceptual recognition tasks, e.g. recognizing a well-recognized face embedded in an unfamiliar scene, in approximately 100-200ms, whereas tasks of a lot lesser complexity may take days on a regular computer. A neural community is a laptop that is designed to lay out the way in which where the brain performs a special assignment. The network is implemented through utilizing electronic components or is simulated in software on a digital computer. A neural community is a vastly parallel distributed processor made up of simple processing units, which has a common propensity for storing experimental abilities and making it to be had to be used. It resembles the mind in two respects: 1) Knowledge is attained by using the network from its atmosphere by a training process. 2) Interneuron connection strengths, often called synaptic weights, are used to store the attained knowledge.

Neural networks, with their amazing potential to derive that means from problematic or imprecise information, can be used to extract patterns and observe trends that are too difficult to be observe by either people or different computer strategies. Other benefit consists: 1) Adaptive learning: An ability to learn tips on how to do duties depend on the data given for training or preliminary experience. 2) Selforganization: An ANN can create its own organization or representation of the information it receives throughout learning time. 3) Real Time Operation: ANN computations can also he implemented in parallel, and certain hardware gadgets are being designed and manufactured which take benefit of this capability.

The human nervous system can be divided into three stages that can be defined as follows:

Fig 2.3: Block diagram representation of human nervous system

The receptors acquire information from the atmosphere. The effectors generate interactions with the environment e.g. activate muscles. The drift of knowledge/activation is represented by using arrows in fig.2.3.

There are roughly 10 billion neurons in the human cortex. Each biological neuron is hooked up to several thousands of other neurons. The common operating pace of biological neurons is measured in milliseconds. Nearly all of neurons encode their activations or outputs as a series of brief electrical pulses. The neuron's nucleus includes the incoming activations and converts them into output activations. The neurons nucleus includes the genetic material within the form of DNA. This exists in most types of cells. Dendrites are fibers which emanate from the cell body and furnish the receptive zones that acquire activation from other neurons. Axons are fibers appearing as transmission lines that ship activation to different neurons. The junctions that enable signal transmission between axons and dendrites are referred to as synapses

#### 2) Training of Artificial Neural Networks

A neural network must be configured such that the application of a set of inputs produces (either 'direct' or through a relaxation system) the required set of outputs. Various ways are there to set the strengths of the connections exist. A technique is to set the weights explicitly, utilizing a priori potential. Yet another method is to train the neural network through feeding it instructing patterns and letting it exchange its weights according to a few training rule.

### III. IMPLEMENTATION OF ANN BASED CONTROL SCHEME

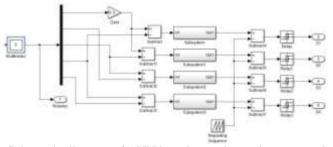

In out proposed circuit, the error generated while comparing instantaneous capacitor voltages with reference magnitude in TLBC is given as input to an artificial neural network based controller shown in Fig-3.1. The controller is trained with a set of inputs and target outputs. The trained network is validated with different sets of known inputs. The output of ANN controller gives required modulating signal for generation of hysteresis based PWM signals for usage in active front end circuit.

Fig.3.1: Schematic diagram of ANN based capacitor voltage control circuit

When the proposed ANN is replaced with PI controller, same like the above the error and change in error is given as the input. The error is nothing but the voltage difference between reference voltage and Vc3 for gate signal S1, voltage difference between reference voltage and Vc2 for gate signal S2, voltage differences between Vc2 and Vc1 for gate signal S3 and voltage differences between Vc3 and Vc4 for gate signal S4. The change in change in error is nothing but the dv/dt of the error as shown in the Fig.3.2. For four switches there will four ANN blocks, but all the ANN blocks will be in same structure. So, one of the ANN block is shown below in Fig.3.2.

The ANN block shown in Fig.3.2 is simulated from the NFTOOL from the MATLAB. In the

NFTOOL box training of the network is initiated, the training, validation and testing percentages so that the ANN iterations depending on the percentage values. Here ANNis trained in NFTOOL by keeping 80% training, 10% validation and 10% testing with 10 hidden layers. After the NFTOOL simulates the required ANN block, then it kept in place of PI controller. The output of the ANN block generates the required modulating signals to trigger the switches. For 4 switches there will four ANN blocks simulated by NFTOOL. When the output of the ANN is compared with PI controller, it is clearly observed that ANN has the better output, better response, quick settling time f capacitor voltages. The results of both PI controller and ANN controller out puts are shown in next chapter.

Fig.3.2: Schematic diagram of ANN block in subsystem

Each ANN block contains the following circuit in it as shown in fig.3.3. It contains variable type of limits.

Fig.3.3:Schematic of the ANN block scehemetic diagram

For each ANN block input i.e., error and change in error from capacitor voltages is given as input to the ANN block. These error and change in error values are in range of 10,000 values and are given to NTOOL training.

### IV. RESULTS

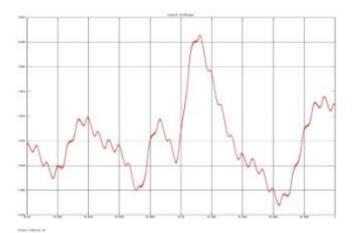

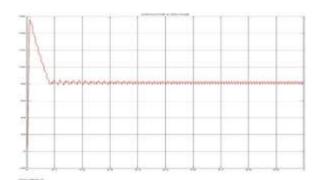

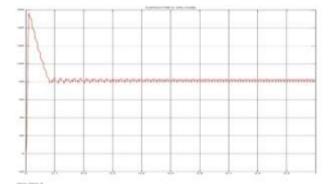

For balancing the capacitor voltages of the TLBC is done by using PI controller. To get the better performance PI controller scheme is replacing with ANN scheme. By introducing the ANN controller, it clearly observed that the response of the NPC multilevel inverter is much better and has quick settling time. The capacitor voltages reach to steady state in less time when compared to the capacitor voltages when PI controller based switching scheme is used for NPC multilevel inverter.

Case studies are performed on ANN based NPC multilevel inverter for different power factors of load and the observations are tabulated in table 4.1.Table 4.1 shows the power factor values for various load inductances and THD in the output voltages and currents. For all cases, capacitor voltages of the TLBC, output voltages and currents are recorded.

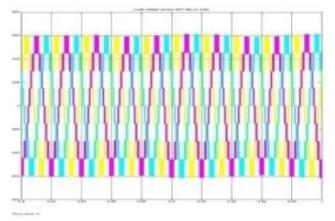

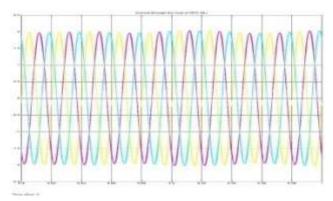

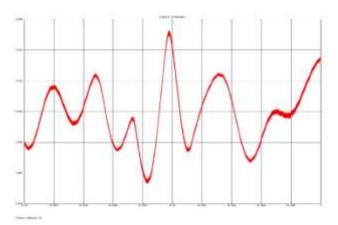

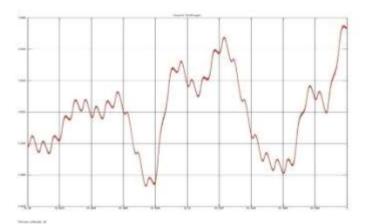

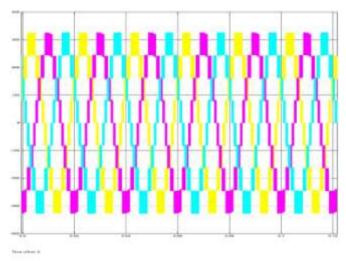

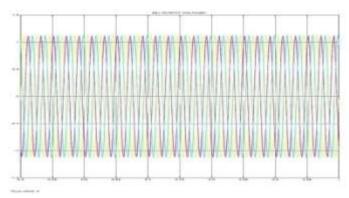

Results shown in fig.4.1 and 4.2 are the voltage across the load and current through the load connected to the NPC multilevel using PI controller.Results shown in fig.4.3 is the TLBC switching triggering circuit and the results shown from fig.4.4 to fig.4.7 are capacitor voltages.

Fig.4.1: Voltage across the NPC multilevel inverter using PI controller

Fig.4.2: Current through the load of NPC using PI controller

Fig.4.3: TLBC switches triggering schematic diagram when PI controller is used.

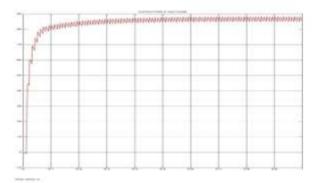

Fig.4.4:Output wave forms of capacitor voltages C1 balanced by PI controller.

Fig.4.5:Output wave forms of capacitor voltages C2 balanced by PI controller.

Fig.4.6:Output wave forms of capacitor voltages C3 balanced by PI controller.

Fig.4.7: Output wave forms of capacitor voltages C4 balanced by PI controller.

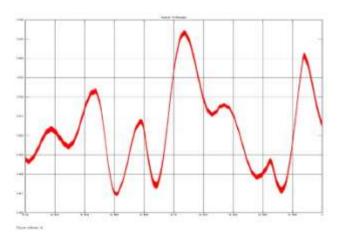

Results shown in fig.4.8 and 4.9 are the voltage across the load and current through the load connected to the NPC multilevel using ANN controller. Results shown in fig.4.10 is the TLBC switching triggering circuit and the results shown from fig.4.11 to fig.4.14 are capacitor voltages.

Fig.4.8: Voltage across the NPC multilevel inverter using ANN controller

Fig.4.9: Current through the NPC multilevel inverter using ANN controller.

Designed of

Fig.4.10: TLBC switches triggering schematic diagram when ANN controller is used.

**Table.4.1:** Case studies of the ANN controlled NPC multilevel inverter.

| S1.N | Power     | THD of the NPC voltage across |         |         | THD of the NPC current through the |         |         |  |

|------|-----------|-------------------------------|---------|---------|------------------------------------|---------|---------|--|

| 0    | factor of | the load (%)                  |         |         | load (%)                           |         |         |  |

|      | Load (PF) | Phase A                       | Phase B | Phase C | Phase A                            | Phase B | Phase C |  |

| 1    | 0.40      | 22.54                         | 22.61   | 22.45   | 3.943                              | 3.796   | 4.046   |  |

| 2    | 0.45      | 22.13                         | 22.19   | 22.04   | 3.795                              | 3.644   | 3.903   |  |

| 3    | 0.50      | 21.68                         | 21.73   | 21.59   | 3.627                              | 3.472   | 3.741   |  |

| 4    | 0.55      | 21.22                         | 21.27   | 21.13   | 3.442                              | 3.282   | 3.565   |  |

| 5    | 0.60      | 20.75                         | 20.78   | 20.65   | 3.241                              | 3.073   | 3.373   |  |

| 6    | 0.65      | 20.26                         | 20.29   | 20.16   | 3.021                              | 2.841   | 3.163   |  |

| 7    | 0.70      | 19.78                         | 18.80   | 19.67   | 2.788                              | 2.596   | 2.940   |  |

| 8    | 0.75      | 19.32                         | 19.32   | 19.21   | 2.541                              | 2.337   | 2.706   |  |

| 9    | 0.80      | 18.89                         | 18.89   | 18.77   | 2.280                              | 2.058   | 2.463   |  |

| 10   | 0.85      | 18.54                         | 18.53   | 18.42   | 2.054                              | 1.827   | 2.279   |  |

| 11   | 0.90      | 18.21                         | 18.17   | 18.07   | 1.904                              | 1.617   | 2.130   |  |

| 12   | 0.95      | 17.86                         | 17.81   | 17.72   | 1.692                              | 1.377   | 1.942   |  |

| 13   | 1.00      | 17.20                         | 17.13   | 17.05   | 27.17                              | 27.33   | 26.93   |  |

Fig.4.11:Output wave forms of capacitor voltages C1 balanced by ANN controller.

Fig.4.12: Output wave forms of capacitor voltages C2 balanced by ANN controller.

| 1  |   |   |      |   |   |

|----|---|---|------|---|---|

| 1ª |   |   |      |   |   |

|    |   |   |      |   |   |

| 1  |   |   |      |   | - |

|    | _ | _ | <br> |   | _ |

|    | _ | _ | <br> | _ | _ |

|    | _ | _ | <br> |   | _ |

|    | _ | _ | <br> |   | _ |

Fig.4.13:Output wave forms of capacitor voltages C3 balanced by ANN controller.

Fig.4.14:Output wave forms of capacitor voltages C4 balanced by ANN controller.

## V. CONCLUSION

Proportional plus Integral based Control scheme and ANN based control scheme for capacitor voltage balancing are analyzed and modeled. The circuits thus modeled are applied to TLBC based five-level neutral point clamped inverter. The performance of the control schemes are compared when the converter is supplying both balanced and unbalanced loads.It has been observed that ANN based gives a better transient as well as study state response when compared with PI controller and achieves.With the help of the proposed ANN controller, voltage balancing of capacitors can be done in better manner.

## BIBLOGRAPHY

- [1] Rosmadi Abdullah, Member, Nasrudin Abd. Rahim, Siti Rohani Sheikh Raihan and Abu Zaharin Ahmad : "Five-Level Diode-Clamped Inverter With Three-Level Boost Converter" IEEE Transactions on Industrial Electronics, Vol. 61, No. 10, October 2014

- [2] Akira Nabae, Isao Takahashi, Hirofumi Akagi: "A new Neutral-Point-Clamped PWM Inverter", IEEE Transaction on Industry Applications, Vol. 1A-17, NO. 5, September/October 1981.

- [3] Ilhami Colak, Ramazan Bayindir and Ersan Kabalci, "Design and analysis of a 7-level cascaded multilevel inverter with dual SDCSs," International Symposium on Power Electronics, Electrical Drives, Automation and Motion, volume 25, no.3, pp.4244-4987, october2010.

- [4] Fang Zheng Peng, Jih-Sheng Lai, John W. McKeever and James Van Coevering, "A multilevel voltage-source inverter with separate DC sources for static var generation," IEEE Transactions on Industry Applications, volume 32, no. 5, September/October 1996.

- [5] K. Sano and H. Fujita, "Voltage-balancing circuit based on a resonant switchedcapacitor converter for multilevel inverters," IEEE Transactions on Industrial Application , volume 44, no. 6, pp. 17681776, November/December 2008.

- [6] A. Ashaibi, S. J. Finney, B. W. Williams, and A. Massoud, "Extend the use of auxiliary circuit to start up, shut down, and balance of the modified diode clamped multilevel inverter," International Conference on Power Electronic Drive System, pp. 10491053, Nov. 2007.

- [7] H.A. Hotait, A.M. Massoud, S.J. Finney and B.W. Williams," Capacitor voltage balancing using redundant states of space vector modulation for five-level diode 42 clamped inverters", The institution of engineering and technology power electronics, volume 3, issue 2, pp. 292313, January 2009.

- [8] K. Gupta and A. M. Khambadkone, "A simple space vector PWM scheme to operate

a three-level NPC inverter at high modulation index including over modulation region, with neutral point balancing," IEEE Transactions on Industry Applications, volume 43, no. 3, pp. 751760, May/June 2007.

- [9] Nabae, I. Takahashi, and H. Akagi. A new neutralpoint clamped PWM inverter. IEEE Trans. Ind. Appl.; IA-17(5):518–523, 1981.

- [10] S. Kouro, M. Malinowski, K. Gopakumar, J. Pou, L. G. Franquelo, B. Wu, J. Rodr'iguez, M. A. P'erez, and J. I. Le'on. Recent advances and industrial applications of multilevel converters. IEEE Trans. Ind. Electron.; 57(8):2553–2580, 2010.

- [11] J. Rodr'iguez, L. G. Franquelo, S. Kouro, J. I. Le'on, R.C. Portillo, M. M. Prats, and M. A. P'erez. Multilevel converters: An enabling technology for high-power applications. Proc. IEEE; 97(11):1786–1817, 2009.

- [12] M. Marchesoni and P. Tenca. Theoretical and practical limits in multilevel MPC inverters with passive front ends. Proc. of the 9th European Conference on Power Electronics and Applications, Graz, Austria, 2001.

- [13] M. Saeedifard, R. Iravani, and J. Pou. Analysis and control of dc-capacitorvoltage-drift phenomenon of a passive frontend five-level converter. IEEE Trans. Ind. Electron.; 54(6):3255–3266, 2007.

- [14] Z. Shu, X. He, Z. Wang, D. Qiu, and Y. Jing. Voltage balancing approaches for diode-clamped multilevel converters using auxiliary capacitor-based circuit. IEEE Trans. Power Electron. 28(5):2111–2124, 2013.

- [15] A. Shukla, A. Ghosh, and A. Joshi. Control schemes for dc capacitor voltages equalization in diode-clamped multilevel inverter-based DSTATCOM. IEEE Trans. Power Del.; 23(2):1139–1149, 2008.

- [16] S. Busquets-Monge, S. Alepuz, J. Bordonau, and J. Peracaula. Voltage balancing control of diode-clamped multilevel converters with passive front-ends. IEEE Trans. Power Electron. 23(4):1751–1758, 2008.

- [17] Chang-Su M., Tae-Jin K., Dae-Wook K., Dong-Seok H., A simple control strategy for balancing the DC-link voltage of neutralpoint-clamped inverter at low modulation index, The 29th Annual Conference of IEEE Industrial Electronics Society, Roanoke, USA, 2003

- [18] Cobreces S., Bordonau J., Salaet J., Bueno E.J., Rodriguez F.J., Exact Linearization Nonlinear Neutral-Point Voltage Control for

Single-Phase Three-Level NPC Converters, IEEE Transactions on Power Electronics, 24 (2009), No. 10, 2357-2362

- [19] Busquets-Monge S., Alepuz S., Rocabert J., Bordonau J., Pulse Width Modulations for the Comprehensive Capacitor Voltage Balance of n-Level Three-Leg Diode-Clamped Converters, IEEE Transactions on Power Electronics, 24 (2009), No. 5, 1364-1375

- [20] Patel P.J., Patel R.A., Patel V., Tekwani P.N., Implementation of Self Balancing Space Vector Switching Modulator for Three-Level Inverter, The 3rd International Conference on Industrial and Information Systems, Kharagpur, India, 2008

- [21] Yamanaka K., Hava A.M., Kirino H., Tanaka Y., Koga N., Kume T., A novel neutral point potential stabilization technique using the information of output current polarities and voltage vector, IEEE Transactions on. Industry Applications, 38 (2002), No. 6, 1572-1580

- [22] Tallam R.M., Naik R., Nondahl T.A., A carrier-based PWM scheme for neutral-point voltage balancing in three-level inverters, IEEE Transactions on Industry Applications, 41 (2005), No. 6, 1734-1743

- [23] Qiang S., Wenhua L., Qingguang Y., Zhonghong W., A neutral-point potential balancing algorithm for three-level NPC inverters using analytically injected zerosequence voltage, The 8th IEEE Annual Conference on Applied Power Electronics, Miami, USA, 2003

- [24] Ogasawara S., Akagi H., Analysis of variation of neutral point potential in neutral-point-clamped voltage source PWM inverters, The 29th Annual Meeting of IEEE Industry Applications Society, Toronto, Canada, 1993

- [25] A Pandey, B N Singh, A Chandra, K Al-Haddad, D P Kothari, A Review of Multilevel Power Converters, IE (I)-EL, vol. 86, pp no. 220-231, March 2006.

- [26] Rodriguez, J.; Jih-Sheng Lai; Fang Zheng Peng; , "Multilevel inverters: a survey of topologies, controls, and applications," Industrial Electronics, IEEE Transactions on , vol.49, no.4, pp. 724-738, Aug 2002

- [27] W. McMurray, —Fast response steppedwave switching power converter circuit, U.S. Patent 3 581 212, May 25, 1971.

- [28] J. A. Dickerson and G. H. Ottaway, —Transformer less power supply with line to load isolation, U.S. Patent 3 596 369, Aug. 3, 1971.

- [29] R. H. Baker, —High-voltage converter circuit, U.S. Patent 4 203 151, May 13, 1980.Nabae, I. Takahashi, and H. Akagi, —A new neutral-point-clamped PWM inverter, IEEE Trans. Ind. Appl., vol. IA-17, no. 5, pp. 518–523, Sep./Oct. 1981.R. H. Baker, —Bridge converter circuit, U.S. Patent 4 270 163, May 26, 1981.

- [30] ABB. [Online]. Available: www.abb.com

- [31] M. M. Renge and H. M. Suryawanshi, "Five-level diode clamped inverter to eliminate common mode voltage and reduce dv/dt in medium voltage rating induction motor drives," IEEE Trans. Power Electron., vol. 23, no. 4, pp. 1598–1607, Jul. 2008.

- [32] M. M. Renge and H. M. Suryawanshi, "Three-dimensional space-vector modulation to reduce common-mode voltage for multilevel inverter," IEEE Trans. Ind. Electron., vol. 57, no. 7, pp. 2324–2331, Jul. 2010.

- [33] K. Hasegawa and H. Akagi, "Lowmodulation-index operation of a five level diode-clamped PWM inverter with a dcvoltage-balancing circuit for a motor drive," IEEE Trans. Power Electron., vol. 27, no. 8, pp. 3495–3504, Aug. 2012.

- [34] K. Hasegawa and H. Akagi, "A new dcvoltage-balancing circuit including a single coupled inductor for a five-level diodeclamped PWM inverter," IEEE Trans. Ind. Appl., vol. 47, no. 2, pp. 841–852, Mar./Apr. 2011.

- [35] H. A. Hotait, A. M. Massoud, S. J. Finney, and B.W.Williams, "Capacitor voltage balancing using redundant states of space vector modulation for five-level diode clamped inverters," IET Power Electron., vol. 3, no. 2, pp. 292–313, Mar. 2010.

- [36] S. Busquets-Monge, J. Rocabert, P. Rodriguez, S. Alepuz, and J. Bordonau, "Multilevel diode-clamped converter for photovoltaic generators with independent voltage control of each solar array," IEEE Trans. Ind. Electron., vol. 55, no. 7, pp. 2713–2723, Jul. 2008.

- [37] E. Ozdemir, S. Ozdemir, and L. M. Tolbert, "Fundamental-frequency modulated sixlevel diode-clamped multilevel inverter for three-phase stand-alone photovoltaic system," IEEE Trans. Ind. Electron., vol. 56, no. 11, pp. 4407–4415, Nov. 2009.

- [38] A. A. Boora, A. Nami, F. Zare, A. Ghosh, and F. Blaabjerg, "Voltagesharing converter to supply single-phase asymmetrical fourlevel diodeclamped inverter with high power factor loads," IEEE Trans. Power Electron., vol. 25, no. 10, pp. 2507–2520, Oct. 2010.

www.ijera.com

- [39] M. Fracchia, T. Ghiara, M. Marchesoni, and M. Mazzucchelli, "Optimized modulation techniques for the generalized N-level converter," in Proc. 23rd IEEE PESC, 1992, vol. 2, pp. 1205–1213.

- [40] M. Saeedifard, R. Iravani, and J. Pou, "Analysis and control of dc capacitorvoltage-drift phenomenon of a passive frontend five-level converter," IEEE Trans. Ind. Electron., vol. 54, no. 6, pp. 3255–3266,Dec. 2007.

- [41] M. Saeedifard, R. Iravani, and P. Josep, "A space vector modulation strategy for a backto-back five-level HVDC converter system," IEEE Trans. Ind. Electron., vol. 56, no. 2, pp. 452–466, Feb. 2009.

- [42] P. Fang Zheng, L. Jih-Sheng, J. McKeever, and J. Van Coevering, "A multilevel voltage-source converter system with balanced dc voltages," in Proc. 26th IEEE PESC, 1995, vol. 2, pp. 1144–1150.

- [43] R. W. Menzies, P. Steimer, and J. K. Steinke, "Five-level GTO inverters for large induction motor drives," IEEE Trans. Ind. Appl., vol. 30, no. 4, pp. 938–944, Jul./Aug. 1994.

- [44] K. Jung-Min, K. Bong-Hwan, and N. Kwang-Hee, "Three-phase photovoltaic system with three-level boosting MPPT control," IEEE Trans. Power Electron., vol. 23, no. 5, pp. 2319–2327, Sep. 2008.

- [45] M. Malinowski, W. Kolomyjski, M. P. Kazmierkowski, and S. Stynski, "Control of variable-speed type wind turbines using direct power control space vector modulated 3-level PWM converter," in Proc. IEEE Int. Conf. Ind. Technol., 2006, pp. 1516–1521.

- [46] M. Hengchun, D. Boroyevich, and F. C. Lee, "Multi-level 2-quadrant boost choppers for superconducting magnetic energy storage," in Proc. Appl. Power Electron. Conf. Expo., 1996, vol. 2, pp. 876–882.

- [47] V. I. Meleshin, D. V. Zhiklenkov, and A. A. Ganshin, "Efficient three-level boost converter for various applications," in Proc. Power Electron. Motion Control Conf., 2012, pp. DS1e.9-1–DS1e.9-8

- [48] C. Newton, M. Sumner, and T. Alexander, "The investigation and development of a multi-level voltage source inverter," in Proc. 6th Int. Conf. Power Electron. Variable Speed Drives, 1996, pp. 317–321.

- [49] S. Alepuz, S. Busquets-Monge, J. Bordonau, J. Gago, D. Gonzalez, and J. Balcells, "Interfacing renewable energy sources to the utility grid using a three-level inverter," IEEE Trans. Ind. Electron., vol. 53, no. 5, pp. 1504–1511, Oct. 2006.

- [50] S. A. Khajehoddin, A. Bakhshai, and P. K. Jain, "A simple voltage balancing scheme for m-level diode-clamped multilevel converters based on a generalized current flow model," IEEE Trans. Power Electron., vol. 23, no. 5, pp. 2248–2259, Sep. 2008.

- [51] S. Busquets-Monge, S. Alepuz, J. Bordonau, and J. Peracaula, "Voltage balancing control of diode-clamped multilevel converters with passivefront-ends," IEEE Trans. Power Electron., vol. 23, no. 4, pp. 1751–1758, Jul. 2008.

- [52] S. Busquets-Monge, J. Bordonau, and J. Rocabert, "A virtual-vector pulse width modulation for the four-level diode-clamped dc-ac converter," IEEE Trans. Power Electron., vol. 23, no. 4, pp. 1964–1972, Jul. 2008.

- [53] S. Busquets-Monge, S. Alepuz, J. Rocabert, and J. Bordonau, "Pulse width modulations for the comprehensive capacitor voltage balance of n-level three-leg diode-clamped converters," IEEE Trans. Power Electron., vol. 24, no. 5, pp. 1364–1375, May 2009.

- [54] A. Von Jouanne, D. Shaoan, and Z. Haoran, "A multilevel inverter approach providing dc-link balancing, ride-through enhancement, and common-mode voltage elimination," IEEE Trans. Ind. Electron., vol. 49, no. 4, pp. 739–745, Aug. 2002.

- [55] K. Amei, Y. Takayasu, T. Ohji, and M. Sakui, "A maximum power control of wind generator system using a permanent magnet synchronous generator and a boost chopper circuit," in Proc. Power Convers. Conf., 2002, vol. 3, pp. 1447–1452.

- [56] Hao Yu, Auburn University and Bogdan M.Wilamowski, Auburn University "Levenberg–Marquardt Training".